Intel’s Take on the Next Wave of Moore’s Law

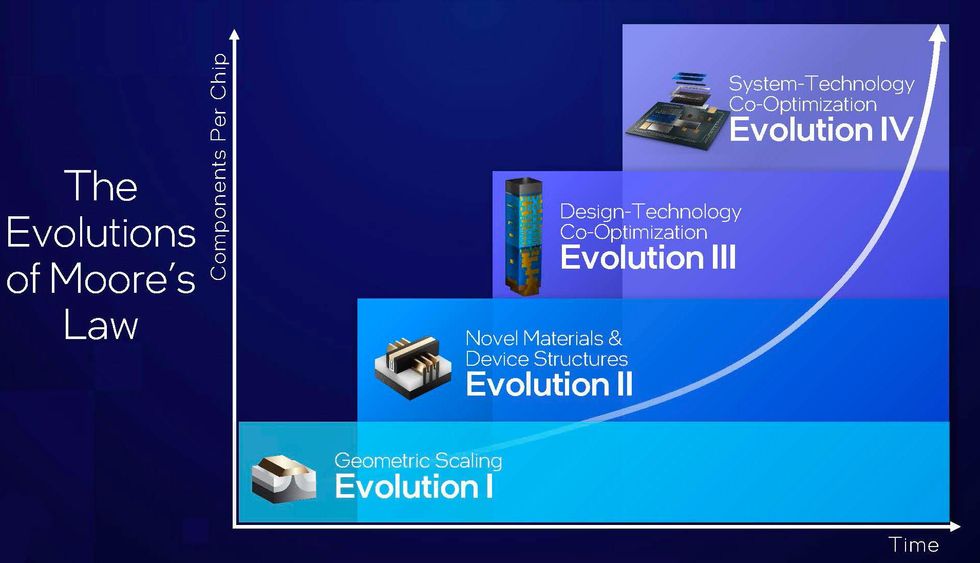

The next wave of Moore’s Law will rely on a developing concept called system technology co-optimization, said Ann B. Kelleher, general manager of technology development at Intel in an interview with IEEE Spectrum ahead of her plenary talk at the 2022 IEEE Electron Device Meeting (IEDM).

“Moore’s Law is about increasing the integration of functions,” says Kelleher. “As we look forward into the next 10 to 20 years, there’s a pipeline full of innovation” that will continue the cadence of improved products every two years. That path includes the usual continued improvements in semiconductor processes and design, but system technology co-optimization (STCO) will make the biggest difference.

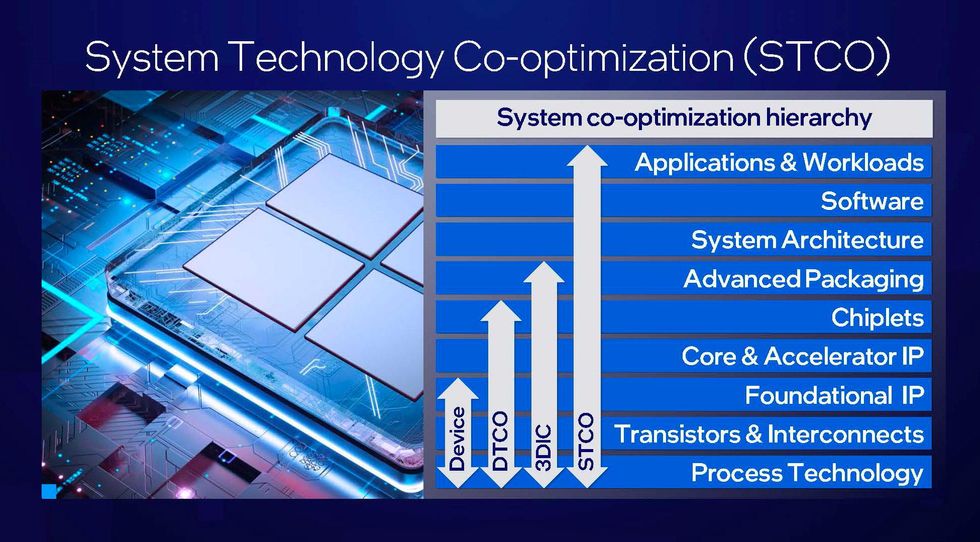

Kelleher calls it an “outside-in” manner of development. It starts with the workload a product needs to support and its software, then works down to system architecture, then what type of silicon must be within a package, and finally down to the semiconductor manufacturing process. “With system technology co-optimization, it means all the pieces are optimized together so that you’re getting your best answer for the end product,” she says.

STCO is an option now in large part because advanced packaging, such as 3D integration, is allowing the high-bandwidth connection of chiplets—small, functional chips—inside a single package. This means that what would once be functions on a single chip can be disaggregated onto dedicated chiplets, which can each then be made using the most optimal semiconductor process technology. For example, Kelleher points out in her plenary that high-performance computing demands a large amount of cache memory per processor core, but chipmaker’s ability to shrink SRAM is not proceeding at the same pace as the scaling down of logic. So it makes sense to build SRAM caches and compute cores as separate chiplets using different process technology and then stitch them together using 3D integration.

A key example of STCO in action, says Kelleher, is the Ponte Vecchio processor at the heart of the Aurora supercomputer. It’s composed of 47 active chiplets (as well as 8 blanks for thermal conduction). These are stitched together using both advanced horizontal connections (2.5D packaging tech) and 3D stacking. “It brings together silicon from different fabs and enables them to come together so that the system is able to perform against the workload that it’s designed for,” she says.

At IEDM, Intel engineers will report that they’ve increased the density of their 3D hybrid bonding technology tenfold versus what they reported in 2021. Increased connection density means more chip functions can be disaggregated onto separate chiplets, in turn providing more potential to use STCO to improve outcomes. Hybrid bond pitches, meaning the distance between the interconnects, are just 3 micrometers with this new technology. With that, even more cache can be separated from the processor cores. Reducing the bond pitch to between 2 micrometers and 100 nanometers could mean being able to start pulling apart logic functions that today must be on the same piece of silicon, according to Kelleher.

The drive to optimize systems by disaggregating functions is having consequences for future semiconductor manufacturing processes. Future semiconductor process technology has to contend with the thermal stresses of a 3D-packaged environment. But interconnect technology will probably see the biggest change. Kelleher says Intel is on track to introduce a technology it calls PowerVia (backside power delivery, more generally) in 2024. PowerVia moves a chip’s power delivery network beneath the silicon, reducing the size of logic cells and cutting power consumption. But it also “gives us different opportunities in terms of what we can and how we can interconnect in the package,” says Kelleher.

Kelleher stresses that STCO is still in its infancy. Electronic design automation (EDA) tools have already tackled STCO’s predecessor, design technology co-optimization (DTCO), which focuses on logic-cell level and functional-block level optimizations. “But some of the EDA tool vendors are already working on this,” she says. “Going forward, the focus is going to be on the methods and tools that help enable STCO.”

As STCO develops, device engineers may have to develop with it. “Generally, engineers will need to continue to have their device knowledge but also begin to understand the use cases of their technology and their devices,” says Kelleher. “More interdisciplinary skills will be required as we head into more of an STCO world.”

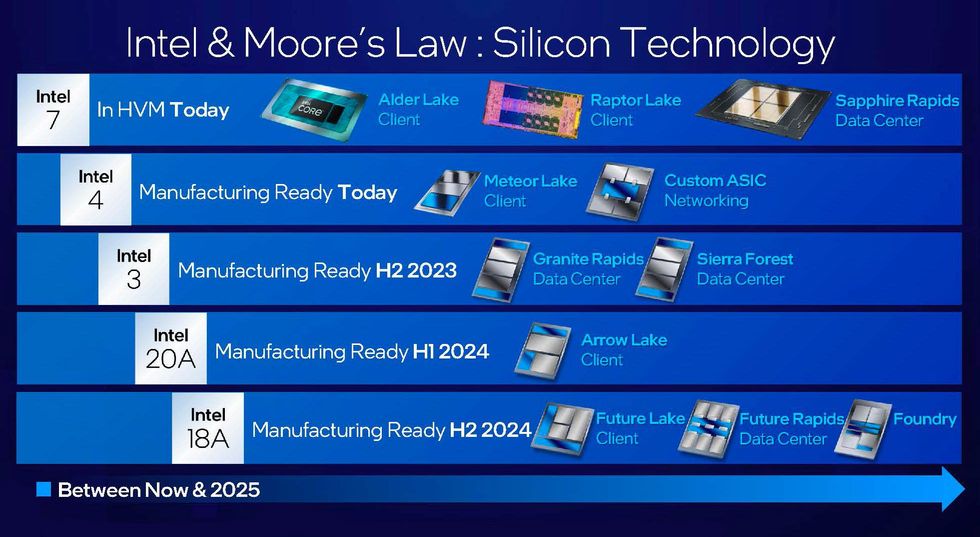

Intel’s Road Map

Kelleher also updated Intel’s road map, tying it in with the progression of Moore’s Law and the evolution of the device since the invention of the first transistor. The bottom line is that things are on track from when Intel announced its new manufacturing road map less than two years ago, according to Kelleher. But she did fill in some details of which processors would debut with the new tech.

Intel 20A, due for manufacturing introduction in the first half of 2024, remains the big technological jump. It simultaneously introduces a new transistor architecture—RibbonFET (more generally called gate-all-around or nanosheet transistors)—and PowerVia backside power delivery. Asked about the risk involved, Kelleher explained the strategy.

“They do not have to be done at once, but we see significant benefits from moving to PowerVia to enable the [RibbonFET] technology,” she says. The development is happening in parallel to reduce the risk of delays, she explains. Intel is running a test process using FinFETs, the transistor architecture in use today, with PowerVia. “That has been working very successfully and it has enabled us to accelerate our development work,” she says.

The Transistor of the Future

Kelleher’s talk comes as the IEEE Electron Device Society celebrates the 75th anniversary of the invention of the transistor. At IEEE Spectrum, we asked experts what the transistor might be like on its 100th birthday in 2047. Kelleher’s take took in the long lifetimes of transistor technology, noting that the planar transistor design lasted from 1960 to about 2010, and that its successor the FinFET is still going strong. “Now we’re going to the RibbonFET which is going to last for probably another 20-plus years…so I expect we’re going to be somewhere with stacked RibbonFETs,” she suggested. [Intel engineers describe that technology in the December 2022 issue of IEEE Spectrum.] However, by that time, the ribbons may be made of 2D semiconductors instead of silicon.

From Your Site Articles

Related Articles Around the Web